Seat No.: Enrolment No.

## GUJARAT TECHNOLOGICAL UNIVERSITY

BE - SEMESTER - VI EXAMINATION - WINTER 2015

Date:14/12/2015 Subject Code: 161004

Subject Name: VLSI Technology and Design

**Total Marks: 70** Time: 2:30pm to 5:00pm

**Instructions:**

- 1. Attempt all questions.

- 2. Make suitable assumptions wherever necessary.

- 3. Figures to the right indicate full marks.

- (a) Derive the expression of threshold voltage of an n-channel 07 **Q.1** MOSFET.

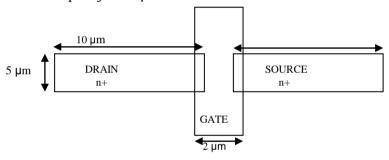

- Consider the n-channel enhancement-type MOSFET shown 07 below. The process parameters are given as follows:

Substrate doping  $N_A = 2 \times 10^{15} \text{ cm}^{-3}$

Source/drain doping  $N_D = 10^{19}$  cm<sup>-3</sup>

Sidewall (p+) doping  $N_A$  (sw) = 4 x  $10^{16}$  cm<sup>-3</sup>

Gate oxide thickness to x = 45 nm

Junction depth  $x_i = 1.0 \mu m$

The substrate is biased at 0V. Assume that the drain voltage is changing from 0.5 V to 5 V, find the average drainsubstrate junction capacitance Cdb.

- (a) Discuss the effect of Full scaling(constant-Field scaling) on: **Q.2** 07

- (i) C<sub>ox</sub> (iii) P (ii) I<sub>D</sub>

- (iv) Power Density 07

- **(b)** Explain the following:

- (i)Channel length modulation

- (ii)Substrate bias effect

## OR

- (b) Draw a typical test circuit arrangement for the measurement 07 of kn ,  $V_{TO}$  and  $\gamma$  of an n-channel MOSFET. Explain how the parameters are measured.

- Define the critical voltage levels of an inverter and also **Q.3 07** (a) define the noise margins of an inverter.

- **(b)** Derive the expression of  $\tau_{PHL}$  of a CMOS inverter.

- (a) Derive the expression of V<sub>OH</sub>, V<sub>OL</sub>, V<sub>IL</sub>, V<sub>IH</sub> of a resistive-Q.3 load inverter.

- Prove that oscillation frequency of a CMOS ring oscillator **07** is inversely proportional to the propagation delay of the inverter.

- (a) Write a short note on CMOS Transmission gate. **Q.4**

07

(b) Draw the circuit diagram of a CMOS edge-triggered D- 07 latch and explain. (a) Explain the estimation of interconnect parasitics. **Q.4 07** (b) Discuss the effect of charge storage and charge leakage in 07 pass transistor circuits. **Q.5** (a) Discuss the on-chip clock generation and distribution. **07** (b) Explain the basic process flow of fabrication of the n-MOS 07 transistor with neat sketches. OR

(a) Discuss various packaging technology used for VLSI chips. Q.5 **07** (b) Explain the Built-In-Self-Test techniques to test VLSI 07 circuit.

\*\*\*\*\*