Enrolment No.

Date:17/05/2016

**Total Marks: 70**

# **GUJARAT TECHNOLOGICAL UNIVERSITY**

## ME - SEMESTER I (NEW) - • EXAMINATION - SUMMER 2016

Subject Code: 2712602 Subject Name: CMOS CIRCUIT DESIGN-I Time:02:30 pm to 05:00 pm Instructions:

- 1. Attempt all questions.

- 2. Make suitable assumptions wherever necessary.

- 3. Figures to the right indicate full marks.

- Q.1 (a) Explain in detail power consumption in CMOS Gates. Discuss Static & 07 Dynamic power dissipation in CMOS Circuits.

- (b) Derive voltage gain Av, output resistance Rout and 3-db Bandwidth equations 07 for Source follower.

- Q.2 (a) Explain Differential amplifier with current mirror load. 07

- (b) Explain need of transistor matching in case of current mirror and discuss 07 different layout techniques.

### OR

- (b) Write short note on MOS device capacitances. 07

- Q.3 (a) Explain Miller Compensation for CMOS Op-Amp.07(b) Define the following with respect to Differential Amplifier.07

- (b) Define the following with respect to Differential Amplifier.

(i) CMRR (ii) ICMR (iii) Output Offset Voltage (iv) PSRR

(v) Differential Mode Voltage (vi) Common Mode Voltage (vii) Slew Rate.

## OR

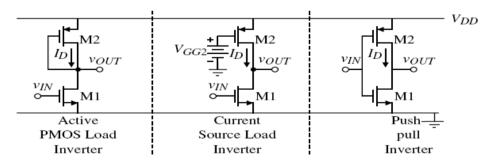

Q.3 (a) Find the small-signal voltage gain and the -3dB frequency in Hertz for the 07 active-load inverter, the current source inverter and the push-pull inverter if  $W_1$  = 2µm,  $L_1 = 1µm$ ,  $W_2 = 1µm$ ,  $L_2 = 1µm$  and the dc current is 50µA. Assume that  $C_{gd1} = 4fF$ ,  $C_{bd1} = 10fF$ ,  $C_{gd2} = 4fF$ ,  $C_{bd2} = 10fF$  and  $C_L = 1pF$ .

- (b) Discuss in brief Mixed Signal VLSI issues in CMOS Technologies. 07

- Q.4(a) Explain in detail Wilson Current Mirror.07(b) List complete classification of CMOS Op-Amps and explain Two Stage CMOS07

ORQ.4(a) Explain in brief Slew Rate of the Differential Amplifier.07(b) Explain in brief an intuitive method of small signal analysis.07Q.5(a) Explain in brief second order effects.07

(b) Discuss Gilbert cell and voltage headroom.

Op-Amp in brief.

07

#### OR

- Q.5 (a) Design the currents and W/L values of the current mirror load differential 07 amplifier to satisfy the following specifications:  $V_{DD}=-V_{SS}=2.5V$ , SR  $\geq 10V/\mu s$  (C<sub>L</sub>=5pf), f<sub>-3db</sub>  $\geq 100KHz$  (C<sub>L</sub>=5pf), a small signal gain of 100V/V, -1.5V  $\leq ICMR \leq 2.0V$ , P<sub>diss</sub>  $\leq 1mW$ .

- (b) Derive  $I_{D(Sat)}$  and  $I_{D(Lin)}$  for n channel MOSFET.

07

#### \*\*\*\*\*

| Parameter<br>Symbol | Parameter Description                         | Typical Parameter Value                          |                                                  |                  |

|---------------------|-----------------------------------------------|--------------------------------------------------|--------------------------------------------------|------------------|

|                     |                                               | n-Channel                                        | p-Channel                                        | Units            |

| Vn                  | Threshold voltage ( $V_{RS} = 0$ )            | 0.7 ± 0.15                                       | -0.7 ± 0.15                                      | v                |

| K"                  | Transconductance parameter<br>(in saturation) | $110.0 \pm 10\%$                                 | 50.0 ± 10%                                       | μΑ/ν             |

| γ                   | Bulk threshold parameter                      | 0.4                                              | 0.57                                             | V <sup>1/2</sup> |

| x.                  | Channel length modulation<br>parameter        | $0.04 (L = 1 \ \mu m)$<br>$0.01 (L = 2 \ \mu m)$ | $0.05 (L = 1 \ \mu m)$<br>$0.01 (L = 2 \ \mu m)$ | v-1              |

| 2   <b>\$</b> _F    | Surface potential at strong inversion         | 0.7                                              | 0.8                                              | v                |