## **GUJARAT TECHNOLOGICAL UNIVERSITY**

ME - SEMESTER II (NEW) - • EXAMINATION - SUMMER 2016 Date: 31/05/2016 Subject Code: 2724204 Subject Name: HDL Based Design with Programmable Logic Time: 10:30 am to 01:00 pm **Total Marks: 70** Instructions: 1. Attempt all questions. 2. Make suitable assumptions wherever necessary. 3. Figures to the right indicate full marks. **O**. 1 1 Which one of the following is not the fundamental VHDL unit? 14 ENTITY A. ARCHITECTURE B. C. LIBRARY **FUNCTION** D. 2 Identify the concurrent statement among the following VHDL constructs. PROCESS A. Β. LOOP C. CASE D. BLOCK The empty sensitivity list in the process statement is identical to \_\_\_\_\_. 3 WAIT ON A. B. WAIT FOR C. WAIT UNTILL D. WAIT In VHDL, the mode of a port does not define 4 A. AN INPUT B. AN OUTPUT AN INPUT AND OUTPUT C. THE TYPE OF THE BIT D. 5 Which of the following is having fine grained architecture? FPGA A. B. CPLD C. ROM D. PAL Which of the following does not belongs to Design Quality? 6 RELIABILITY A. UPGRADIBILITY B. C. GATE LEVEL DESIGN D. MANUFACTURIBILITY 7 Which one of the following is not an EDA tool? XILINX ISE A. B. ALTERA QUARTUS LEONARDO SPECTRUM C. D. MATLAB For designing higher end DSP processor, which of the following design 8 methodology will be most suitable? FULL CUSTOM A. STANDARD CELL B. C. GATE ARRAY **FPGA** D. If the declarative part in the architecture of a half adder is as below 9 component XOR2 port (X,Y:in BIT;z: out BIT); end component

component AND2

port (L,M:in BIT;z:out BIT);

end component

Then what kind of architecture is it?

- A. BEHAVOURIAL

- B. STRUCTURAL

- C. DATAFLOW

- D. NONE OF THESE

- 10 Which statement is used to terminate the current loop iteration and proceed on the next iteration

- A. NEXT

- B. EXIT

- C. BOTH OF THESE

- D. NONE OF THESE

- 11 Which of these is a valid identifier in VHDL?

- A. \_c5

- В. 5с

- C. c 5

- D. process

- 12 The complex programmable logic device (CPLD) contains several PLD blocks and:

- A. field-programmable switches

- B. AND/OR arrays

- C. A global interconnection matrix

- D. A language compiler

- 13 The difference between a PLA and a PAL is:

- A. the PLA has a programmable OR plane and a programmable AND plane, while the PAL only has a programmable AND plane

- B. the PAL has a programmable OR plane and a programmable AND plane, while the PLA only has a programmable AND plane

- C. the PAL has more possible product terms than the PLA

- D. PALs and PLAs are the same thing

- 14 FPGA device XC3S500E-4 has logic density of \_\_\_\_\_ logic gates.

- A. 500

- B. 50,000

- C. 50K

- D. None of the above

- Q.2 (a) 1. What are the different levels of abstraction in VLSI design? Discuss pros and 04 cons of each one of them.

- 2. Identify the operation of the below given VHDL code.

03

ARCHITECTURE dff OF dff IS

BEGIN

bl: BLOCK (clk'EVENT AND clk='1')

BEGIN

q <= GUARDED '0' WHEN rst='1' ELSE d;

END BLOCK b1;

END dff;</pre>

(b) Explain, what functionality following VHDL code does implement? Use 07 diagrams wherever needed.

ENTITY system IS PORT ( in\_data : IN BIT\_VECTOR ( 3 DOWNTO 0 ); out\_data : OUT BIT\_VECTOR ( 3 DOWNTO 0 ); in\_ready, out\_receivedt : IN BIT; in\_received, out\_ready : OUT BIT );

END system;

```

ARCHITECTURE behavioral OF system IS

SIGNAL buffer full, buffer picked : BIT := '0';

SIGNAL word_buffer : BIT_VECTOR ( 15 DOWNTO 0);

BEGIN

a talk: PROCESS ()

VARIABLE count : INTEGER RANGE 0 TO 4 := 0;

BEGIN

WAIT UNTIL in ready = '1';

\operatorname{count} := \operatorname{count} + 1;

CASE count IS

WHEN 0 \Rightarrow NULL;

WHEN 1 => word_buffer ( 3 DOWNTO 0) <= in_data;

WHEN 2 => word_buffer ( 7 DOWNTO 4) <= in_data;

WHEN 3 => word_buffer (11 DOWNTO 8) <= in_data;

WHEN 4 => word buffer (15 DOWNTO 12) <= in data;

buffer full <= '1';

WAIT UNTIL buffer picked = '1';

buffer_full <= '0';</pre>

\operatorname{count} := '0';

END CASE;

in received \leq '1':

WAIT UNTIL in ready = '0';

in received \leq 0;

END PROCESS a talk;

b_talk: PROCESS ()

BEGIN

IF buffer full = '0' THEN WAIT UNTIL buffer full = '1'; END IF;

out data <= word buffer;

buffer picked \leq '1';

WAIT UNTIL buffer full = '0';

buffer picked \leq 0;

out ready \leq '1';

WAIT UNTIL out received = '1';

out ready \leq 0';

END PROCESS b_talk;

```

END behavioral;

### OR

(b) Using several instances of the T flip-flop and simple gates supplied below, which 07 are available in the WORK library in dataflow architecture. Design and implement a 4-bit binary up counter in VHDL using the code template provided.

The counter should have an asynchronous RESET. The counter keeps counting when the active high input signal START is asserted. The counter should generate an active high DONE signal when a total of 10 clock cycles are counted.

-----

The entity declarations for the components are given below.

ENTITY t\_ff IS PORT ( t, clk, rst : IN BIT; q, qb : OUT BIT ); END t\_ff; ENTITY and IS PORT ( i1, i2 : IN BIT; o1 : OUT BIT ); END and 2; ENTITY and IS PORT ( i1, i2, i3 : IN BIT; o1 : OUT BIT ); END and 3; ENTITY and IS PORT ( i1, i2, i3, i4 : IN BIT; o1 : OUT BIT ); END and 4; ENTITY or2IS PORT ( i1, i2 : IN BIT; o1 : OUT BIT ); END or2;ENTITY or3IS PORT ( i1, i2, i3 : IN BIT; o1 : OUT BIT ); END or3;ENTITY or4IS PORT ( i1, i2, i3, i4 : IN BIT; o1 : OUT BIT ); END or4;ENTITY xor2IS PORT ( i1, i2 : IN BIT; o1 : OUT BIT ); END xor2;ENTITY not1IS PORT ( i1, i2 : IN BIT; o1 : OUT BIT ); END not1;

# CODE TEMPLATE

| ENTITY counter4 IS                                   |

|------------------------------------------------------|

| PORT ( reset, start, clk : IN BIT; done : OUT BIT ); |

| END counter4;                                        |

ARCHITECTURE structural OF counter 4 IS

COMPONENT

IS

PORT (\_\_\_\_\_\_: IN BIT; \_\_\_\_\_: OUT BIT );

END COMPONENT;

COMPONENT \_\_\_\_\_\_ IS

PORT (\_\_\_\_\_\_: IN BIT; \_\_\_\_\_: OUT BIT );

END COMPONENT;

COMPONENT \_\_\_\_\_\_ IS

PORT (\_\_\_\_\_\_: IN BIT; \_\_\_\_\_\_: OUT BIT );

END COMPONENT;

DECLARE YOUR SIGNALS HERE BEGIN INST0: \_\_\_\_\_ PORT MAP ( \_\_\_\_\_\_); INST1: \_\_\_\_\_ PORT MAP ( \_\_\_\_\_\_);

END structure;

Q.3 (a) Realize following functions using PLA. What is the total number of programming links required?

.

.

$$F_1 = \sum(0,2,4,6)$$

$$F_2 = \sum(1,3,5,7)$$

$$F_3 = \sum(0,2,5,7)$$

$$F_4 = \sum(4,6,1,3)$$

(b) Draw and explain the basic architecture of an FPGA. Enlist the features available 07 in current generation of FPGA.

#### OR

Q.3 (a) Implement following Boolean equations using PAL. How many total 07 programmable links required? How many of them are fused out to implement the given digital logic?

$$P(A, B, C, D) = \sum m(2,12,13)$$

$$Q(A, B, C, D) = \prod M (0,1,2,3,4,5,6)$$

$$R(A, B, C, D) = \prod M (1,9,12,13,14)$$

$$S(A, B, C, D) = \sum m(1,2,8,12,13)$$

(b) Draw and explain the basic building block of any CPLD device.

07

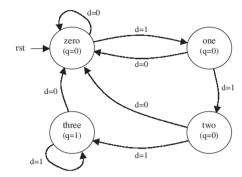

- Q.4 (a) For the state machine given below,

- (i) Identify whether is it a Melay or a Moore Machine?

- (ii) Write the VHDL description

- (iii) Draw the output waveform w.r.t. the clock if the input sequence is 011111100.

- (b) 1. Explain following terms in reference to Digital Design.

- I. High Level Synthesis

- II. RTL Synthesis

- III. Gate Level Synthesis

- 2. Mention various verification techniques used at different VLSI design 04 abstraction levels. Describe static timing analysis and its objective in brief.

#### OR

- Q.4 (a) Define Event-Driven Simulator and Cycle-Based Simulators. What are the pros 07 and cons of the two? Describe the operation of Event Based Simulator with suitable example.

- (b) 1. Differentiate between 'EVENT' and 'TRANSACTION' with the help of 02 suitable example.

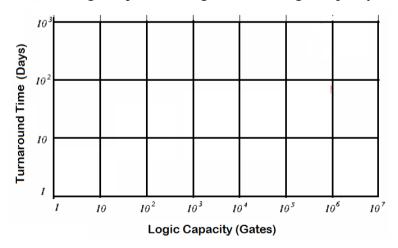

- 2. Map various logic design styles (SSI, SPLD, CPLD, FPGA, Standard-cell, 05 Full Custom) on the given plot of Design Time → Logic Capacity

Q.5 (a) 1. Discuss the use of following Verilog constructs/operator.

04

- a) Module

- b) Wire

- c) Reg

- d) Assign

03

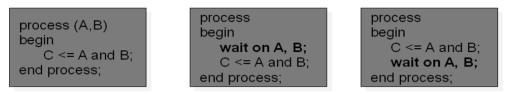

2. The use of explicit and implicit wait statement is presented below.

Assume that all processes are initialized before simulation, which means that they are already running until the first wait condition is met. Also assume std\_logic data type for each of the signal above.

Given this fact, what is the value on C at simulation time zero in each case?

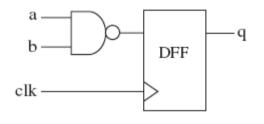

(b) Write the VHDL Test Bench to test the functionality of the below given digital 07 circuit.

## OR

| Q.5 | (a) | 1. Discuss various LOOP structures available in VHDL. Also mention                    | 05 |

|-----|-----|---------------------------------------------------------------------------------------|----|

|     |     | a) How a loop can skip iteration?                                                     |    |

|     |     | b) How the control can exit from the loop?                                            |    |

|     |     | 2. What are the salient differences in Verilog against VHDL? Mention any four.        | 02 |

|     | (b) | Draw the RTL of below given VHDL code and write equivalent Verilog code for the same. | 07 |

|     |     | ENTITY sample IS                                                                      |    |

|     |     | PORT (x, y: IN BIT_VECTOR (1 downto 0);                                               |    |

|     |     | c_in : IN BIT;                                                                        |    |

|     |     | sum, c_out : OUT BIT);                                                                |    |

|     |     | END sample;                                                                           |    |

ARCHITECTURE rtl OF sample IS COMPONENT add IS PORT ( a, b : IN BIT; s, c : OUT BIT ); END COMPONENT; SIGNAL p,q,r,s : BIT := '0'; BEGIN add0 : add port map (x(0), y(0), p, q); add1 : add port map (x(1), y(1), r, s); sum <= p XOR r; c\_out <= q AND s; END rd.

END rtl;

\*\*\*\*\*